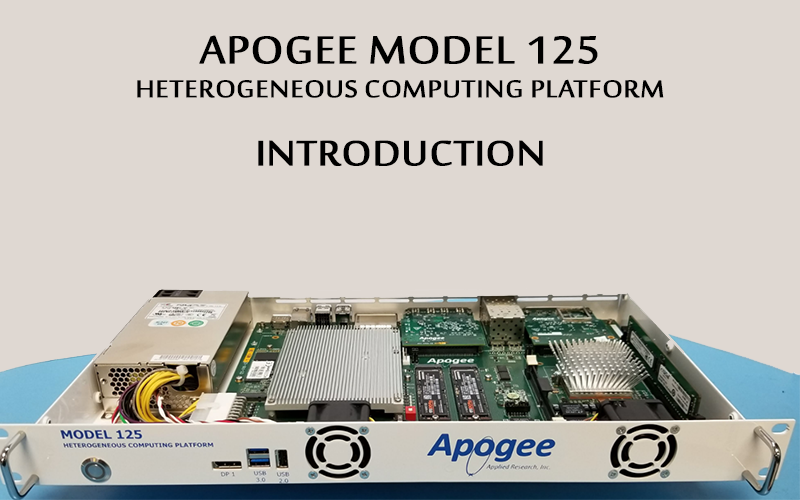

Heterogeneous – adjective – “diverse in character or content” is a great description of the Apogee Model 125. The Model 125 is meant to bridge the gap between large scale FPGA servers / FPGA Boards and smaller Software Defined Radios, SDR Hardware, FPGA Development Board.

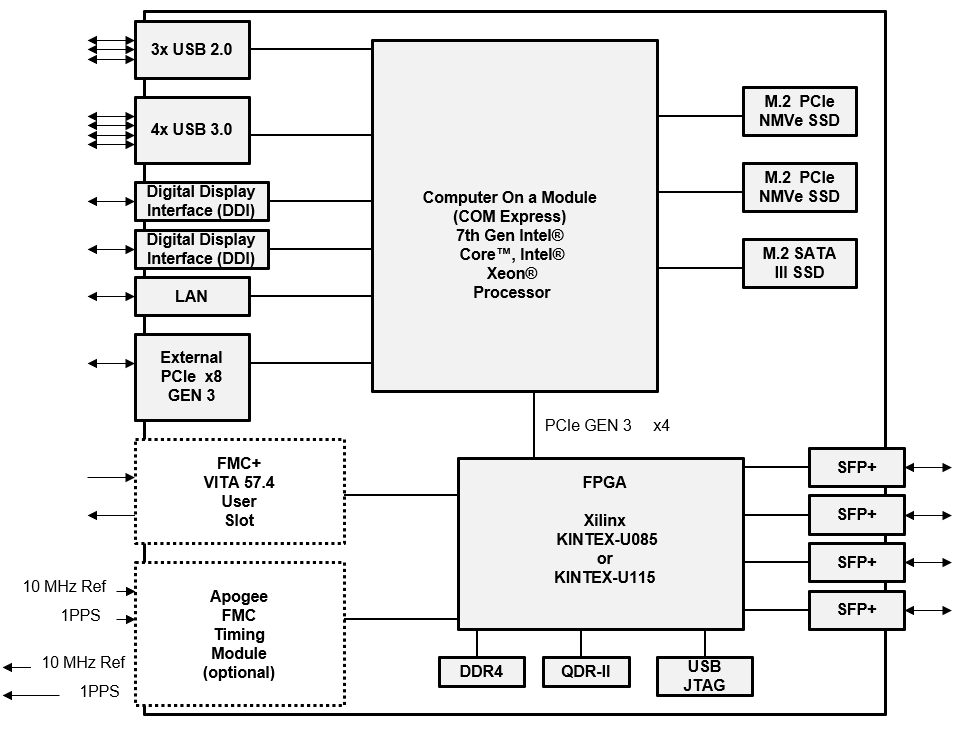

Model 125 Block Diagram

The core components are the Intel® Xeon® Processor E3-1505M v6, 8M Cache, 3.00 GHz, which leads to the Model 125’s diversity with a wide range of I/O options and leveraging a Xilinx KINTEX Ultrascale FPGA. Imagine the possibilities with your IP Core, up to 4TB high-speed internal storage, high-speed DMA between the FPGA and CPU, plus the external PICe x8, SFP+, FMC+ FMC Products, FMC Connector, USB, DSP Programming, and display options.

I/O Highlights:

- 1x FMC+ daughterboard slots (ADC, DAC, Analogue Receiver, Boards Radio, FMC Cards)

- Large customizable Xilinx Ultrascale FPGA for high-performance DSP (KU085 or KU115)

- 4x – 10 GbE SFP+ Ports (RX/TX)

- External PCIe x8 Lane GEN 3

- 2x Digital Display Interface (DDI)

- Up to 4TB High-Speed Internal Storage

- 3x USB 2.0, 4x USB 3.0

- 3x M.2 Solid State Drive (SSD)

- 1x 8GB DDR4 Memory Module

- 1x 72-Mbit QDR® II

- 1x SATA III SSD, 2x PCIe NMVe SSD

- Apogee FMC Timing Module (optional)

- 7th Gen Intel® Core™, Intel® i5, i7 or Xeon® Processor